Download from http://www.engracetech.com

### FUDAN MICROELECTRONICS

# FM4442 256 Bytes Memory Card Chip

Datasheet

Dec. 2008

Future routine revisions will occur when appropriate, without notice. Contact Shanghai Fudan Microelectronics Co., Ltd sales office to obtain the latest specifications and before placing your product order. Please also pay attention to information published by Shanghai Fudan Microelectronics Co., Ltd by various means, including Shanghai Fudan Microelectronics Co., Ltd home page (<u>http://www.fmsh.com/</u>).

Please contact Shanghai Fudan Microelectronics Co., Ltd local sales office for the specification regarding the information in this documents or Shanghai Fudan Microelectronics Co., Ltd products.

#### Trademarks

Shanghai Fudan Microelectronics Co., Ltd name and logo, the "复旦" logo are trademarks or registered trademarks of Shanghai Fudan Microelectronics Co., Ltd or its subsidiaries in China.

Shanghai Fudan Microelectronics Co., Ltd, Printed in the China, All Rights Reserved.

# **Product Overview**

## Description

FM4442 is the memory card chip developed by Shanghai FM Co., Ltd. This chip has 256×8 Bits EEPROM with write protect function and programmable security code. With its contact configuration in accordance to ISO standard 7816 (synchronous transmission), FM4442 can be widely used in different types of IC memory cards.

### **Features**

- 256×8-bits EEPROM organization;

- Byte-wise addressing

- 32×1-bit organization of protection memory

- Irreversible byte-wise write protection of lowest 32 addresses (Byte 0 ... 31)

- Two-wire link protocol

- End of processing indicated at data output

- Answer-to-Reset acc. to ISO standard 7816-3

- Data retention for minimum of ten years

• Programming time 2.5 ms per byte for both erasing and writing

复旦微电子

- Contact configuration and serial interface in accordance with ISO standard 7816 (Synchronous transmission)

- Data can only be changed after entry of the correct 3-byte programmable security code (security memory)

- Compatible SLE4442

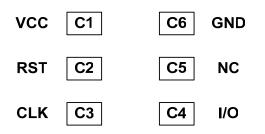

### **Pin Assignment**

## **Pin Function**

| Pin | Symbol | Function                             |

|-----|--------|--------------------------------------|

| C1  | VCC    | Supply voltage 2.5V ~ 5V             |

| C2  | RST    | Reset                                |

| C3  | CLK    | Clock input                          |

| C4  | I/O    | Bidirectional data line (open drain) |

| C5  | NC     | Not Connected                        |

| C6  | GND    | Ground                               |

# **Function Description**

The FM4442 consists of 256 x 8 bits EEPROM main memory and a 32-bit protection memory with PROM functionality. The main memory is erased and written byte by byte. Each of the first 32 bytes can be irreversibly protected against data change by writing the corresponding bit in the protection memory. Each data byte in this address range is assigned to one bit of the protection memory and has the same address as the data byte in the main memory which it is assigned to. Once written the protection bit cannot be erased (PROM).

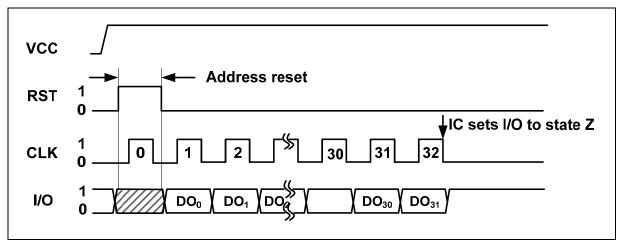

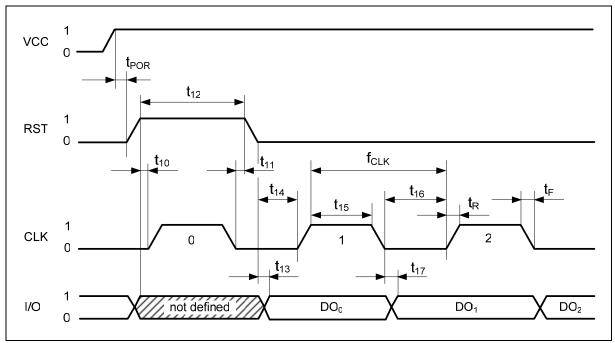

### **Reset and Answer-to-Reset**

Answer-to-Reset takes place according to ISO standard 7816-3 (ATR). The reset can be given at any time during operation. In the beginning, the address counter is set to zero together with a clock pulse and the first data bit (LSB) is output to I/O when RST is set from level H to level L. Under a continuous input of additional 31 clock pulses the contents of the first 4 EEPROM addresses is read out. The 33rd clock pulse switches I/O to high impedance Z and finishes the ATR procedure.

| Answer-to-Reset | Byte1                           | Byte 2                           | Byte 3                            | Byte 4                            |

|-----------------|---------------------------------|----------------------------------|-----------------------------------|-----------------------------------|

| (HEX)           | DO <sub>7</sub> DO <sub>0</sub> | DO <sub>15</sub> DO <sub>8</sub> | DO <sub>23</sub> DO <sub>16</sub> | DO <sub>31</sub> DO <sub>24</sub> |

Figure 2 Reset and Answer-to-Reset

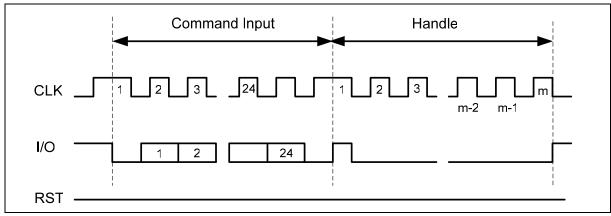

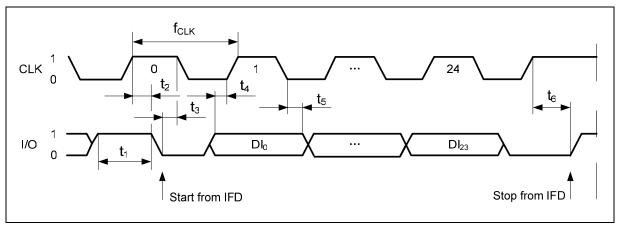

## Commands

Commands Format:

| MS | ISB Control LSB MSB |    | MSB Address LSB |    |    |    |    | MSB Data |    |    | ta | LSB |    |    |    |    |    |    |    |    |    |    |    |

|----|---------------------|----|-----------------|----|----|----|----|----------|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|

| B7 | B6                  | B5 | B4              | B3 | B2 | B1 | B0 | A7       | A6 | A5 | A4 | A3  | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

### **Command Introduction**

### (1) Read Main Memory

|             |    |    |    | Cor | ntrol          |    |                                 |           | Address | Data      |

|-------------|----|----|----|-----|----------------|----|---------------------------------|-----------|---------|-----------|

|             | B7 | B6 | B5 | B4  | B3             | B2 | B1                              | B0        | A7A0    | D7D0      |

| Binary      | 0  | 0  | 1  | 1   | 0              | 0  | 0                               | 0         | Address | No effect |

| Hexadecimal |    |    |    | 30  | Э <sub>н</sub> |    | 00 <sub>н</sub> FF <sub>н</sub> | No effect |         |           |

The command reads out the contents of the main memory (with LSB first) starting at the given byte address (N = 0...255) up to the end of the memory. After the command entry the IFD has to supply sufficient clock pulses. The number of clocks is  $m = (256 - N) \times 8 + 1$ . The read access to the main memory is always possible.

### (2) Read Protection Memory

|             |    |    |    | Cor | ntrol          |    |           |           | Address   | Data      |

|-------------|----|----|----|-----|----------------|----|-----------|-----------|-----------|-----------|

|             | B7 | B6 | B5 | B4  | B3             | B2 | B1        | B0        | A7A0      | D7D0      |

| Binary      | 0  | 0  | 1  | 1   | 0              | 1  | 0         | 0         | No effect | No effect |

| Hexadecimal |    |    |    | 34  | 4 <sub>Н</sub> |    | No effect | No effect |           |           |

The command transfers the protection bits under a continuous input of 32 clock pulses to the output. I/O is switched to high impedance Z by an additional pulse. The protection memory can always be read, and indicates the data bytes of the main memory protected against changing.

### (3) Update Main Memory

|             |    |    |    | Cor | ntrol          |    |                                 |            | Address | Data       |

|-------------|----|----|----|-----|----------------|----|---------------------------------|------------|---------|------------|

|             | B7 | B6 | B5 | B4  | B3             | B0 | A7A0 D7D                        |            |         |            |

| Binary      | 0  | 0  | 1  | 1   | 1              | 0  | 0                               | 0          | Address | Input data |

| Hexadecimal |    |    |    | 38  | 3 <sub>Н</sub> |    | 00 <sub>н</sub> FF <sub>н</sub> | Input data |         |            |

The command programs the addressed EEPROM byte with the data byte transmitted. Depending on the old and new data, one of the following sequences will take place during the processing mode:

- erase and write (5 ms) corresponding to m = 245 clock pulses

- write without erase (2.5 ms) corresponding to m = 124 clock pulses

- erase without write (2.5 ms) corresponding to m = 124 clock pulses

(All values at 50 kHz clock rate.)

Figure 3 Update main memory

### (4) Write Protection Memory

|             |    |    |    | Cor | ntrol |    |                                 |            | Address | Data       |

|-------------|----|----|----|-----|-------|----|---------------------------------|------------|---------|------------|

|             | B7 | B6 | B5 | B4  | B3    | B2 | B1                              | B0         | A7A0    | D7D0       |

| Binary      | 0  | 0  | 1  | 1   | 1     | 1  | 0                               | 0          | Address | Input data |

| Hexadecimal |    |    |    | 30  | Сн    |    | 00 <sub>н</sub> 1F <sub>н</sub> | Input data |         |            |

The execution of this command contains a comparison of the entered data byte with the assigned byte in the EEPROM. In case of identity the protection bit is written thus making the data information unchangeable. If the data comparison results in data differences writing of the protection bit will be suppressed.

### (5) Read Security Memory

|             |    |    |    | Cor | ntrol          |    |    |           | Address   | Data      |

|-------------|----|----|----|-----|----------------|----|----|-----------|-----------|-----------|

|             | B7 | B6 | B5 | B4  | B3             | B2 | B1 | B0        | A7A0      | D7D0      |

| Binary      | 0  | 0  | 1  | 1   | 0              | 0  | 0  | 1         | No effect | No effect |

| Hexadecimal |    |    |    | 3   | 1 <sub>H</sub> |    |    | No effect | No effect |           |

Similar to the read command for the protection memory this command reads out the 4 bytes of the security memory.

#### (6) Update Security Memory

|             |    |                   |   | Cor | ntrol          |   |                                 |            | Address | Data       |

|-------------|----|-------------------|---|-----|----------------|---|---------------------------------|------------|---------|------------|

|             | B7 | B7 B6 B5 B4 B3 B2 |   |     |                |   |                                 | B0         | A7A0    | D7D0       |

| Binary      | 0  | 0                 | 1 | 1   | 1              | 0 | 0                               | 1          | Address | Input data |

| Hexadecimal |    |                   |   | 39  | 9 <sub>Н</sub> |   | 00 <sub>н</sub> 1F <sub>н</sub> | Input data |         |            |

Regarding the reference data bytes this command will only be executed if a PSC has been successfully verified before. Otherwise only each bit of the error counter (Address 0) can be written from "1" to "0". The execution times and the required clock pulses are the same as described under update main memory.

### (7) Compare Verification Data

|             |    |    |    | Cor | ntrol          |    |                                 |            | Address | Data       |

|-------------|----|----|----|-----|----------------|----|---------------------------------|------------|---------|------------|

|             | B7 | B6 | B5 | B4  | B3             | B2 | B1                              | B0         | A7A0    | D7D0       |

| Binary      | 0  | 0  | 1  | 1   | 0              | 0  | 1                               | 1          | Address | Input data |

| Hexadecimal |    |    |    | 3   | 3 <sub>Н</sub> |    | 00 <sub>н</sub> 03 <sub>н</sub> | Input data |         |            |

The command compares one byte of the entered verification data byte with the corresponding reference data byte.

### **PSC** Verification

The FM4442 requires a correct verification of the Programmable Security Code PSC stored in the Security Memory for altering data if desired. The following table gives an overview of the necessary commands for the PSC verification. The sequence of the shaded commands is mandatory.

| Command                   | Control         | Address         | Data            | Remark                                                             |

|---------------------------|-----------------|-----------------|-----------------|--------------------------------------------------------------------|

| Command                   | B7B0            | A7A0            | D7D0            | Keinark                                                            |

| Read security memory      | 31 <sub>H</sub> | No effect       | No effect       | Check error counter                                                |

| Update security memory    | 39 <sub>Н</sub> | 00 <sub>H</sub> | Input data      | Write free bit in error<br>counter input data:<br>0000 0ddd binary |

| Compare verification data | 33 <sub>H</sub> | 01 <sub>H</sub> | Input data      | Reference data byte1                                               |

| Compare verification data | 33 <sub>H</sub> | 02 <sub>H</sub> | Input data      | Reference data byte2                                               |

| Compare verification data | 33 <sub>H</sub> | 03 <sub>H</sub> | Input data      | Reference data byte3                                               |

| Update security memory    | 39 <sub>H</sub> | 00 <sub>H</sub> | FF <sub>H</sub> | Erase error counter                                                |

| Read security memory      | 31 <sub>H</sub> | No effect       | No effect       | Check error counter                                                |

Ü

# **Electrical Characteristics**

# **Absolute Maximum Ratings**

| Parameter           | Symbol           | Min. | Тур. | Max. | Unit |

|---------------------|------------------|------|------|------|------|

| Supply Voltage      | V <sub>CC</sub>  | -0.3 | -    | 6    | V    |

| Input voltage       | Vi               | -0.3 | -    | 6    | V    |

| Storage temperature | T <sub>sto</sub> | -25  | -    | +70  | °C   |

| Power dissipation   | P <sub>tot</sub> | -    | -    | 70   | mW   |

# **Operation Range**

| Parameter           | Symbol          | Min. | Тур. | Max. | Unit |

|---------------------|-----------------|------|------|------|------|

| Ambient temperature | T <sub>A</sub>  | -20  | -    | +60  | °C   |

| Supply Voltage      | V <sub>CC</sub> | 2.5  | 5.0  | 5.5  | V    |

# **DC Characteristics**

| Parameter                                                | Symbol          | Min.    | Тур. | Max.     | Unit |

|----------------------------------------------------------|-----------------|---------|------|----------|------|

| Supply current                                           | I <sub>cc</sub> | -       | 3    | 10       | mA   |

| High level input voltage (I/O, CLK, RST)                 | V <sub>ih</sub> | 0.7 Vcc | -    | Vcc      | V    |

| Low level input voltage (I/O, CLK, RST)                  | V <sub>il</sub> | 0       | -    | 0.3* Vcc | V    |

| High level input current (I/O, CLK, RST)                 | l <sub>h</sub>  | -       | -    | 50       | μA   |

| Low level output current ( $V_{OL} = 0.4V$ , open drain) | I <sub>ol</sub> | 1       | -    | -        | mA   |

| High level output current ( $V_{OH}$ = 5V, open drain)   | I <sub>oh</sub> | -       | -    | 50       | μA   |

| Input capacitance                                        | Ci              | -       | -    | 10       | pF   |

# **AC Characteristics**

| Parameter                                   | Symbol           | Min. | Тур. | Max. | Unit |

|---------------------------------------------|------------------|------|------|------|------|

| CLK Frequency f <sub>CLK</sub>              | f <sub>CLK</sub> | 7    |      | 50   | kHz  |

| I/O High time (Start Condition)             | t <sub>1</sub>   | 10   |      |      | μs   |

| CLK High to I/O Hold time                   | t <sub>2</sub>   | 4    |      |      | μs   |

| I/O Low to CLK Hold time (Start Condition)  | t <sub>3</sub>   | 4    |      |      | μs   |

| I/O Setup to CLK High time                  | t <sub>4</sub>   | 1    |      |      | μs   |

| CLK Low to I/O Hold time                    | t <sub>5</sub>   | 1    |      |      | μs   |

| CLK High to I/O Clear time (Stop Condition) | t <sub>6</sub>   | 4    |      |      | μs   |

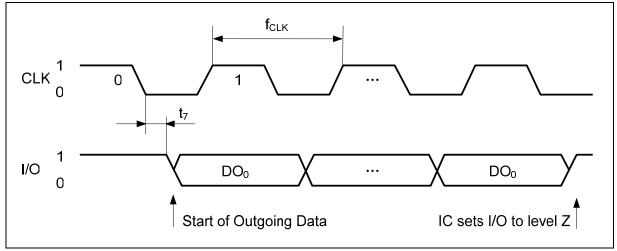

| CLK Low to I/O Valid time                   | t <sub>7</sub>   |      |      | 2.5  | μs   |

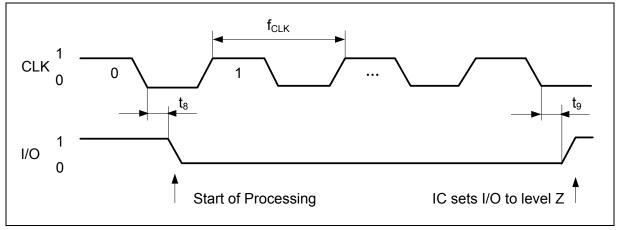

| CLK Low to I/O Valid time                   | t <sub>8</sub>   |      |      | 2.5  | μs   |

| CLK Low to I/O Clear time                   | t <sub>9</sub>   |      |      | 2.5  | μs   |

| RST High to CLK Setup time                  | t <sub>10</sub>  | 4    |      |      | μs   |

| CLK Low to RST Hold time                    | t <sub>11</sub>  | 4    |      |      | μs   |

| RST High time (address reset) time          | t <sub>12</sub>  | 20   | 50   |      | μs   |

| RST Low to I/O Valid time                   | t <sub>13</sub>  |      |      | 2.5  | μs   |

| RST Low to CLK Setup time                   | t <sub>14</sub>  | 4    |      |      | μs   |

### 复旦微电子

Û,

| Parameter                          | Symbol          | Min.                             | Тур. | Max. | Unit |

|------------------------------------|-----------------|----------------------------------|------|------|------|

| CLK High time                      | t <sub>15</sub> | 9                                |      |      | μs   |

| CLK Low time                       | t <sub>16</sub> | 9                                |      |      | μs   |

| CLK Low to I/O Valid time          | t <sub>17</sub> |                                  |      | 2.5  | μs   |

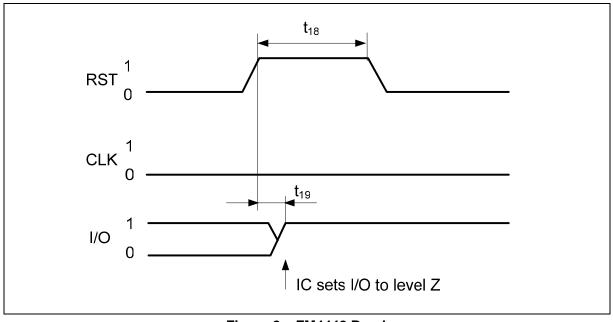

| Reset time for Break               | t <sub>18</sub> | 5                                |      |      | μs   |

| RST High to I/O Clear time (Break) | t <sub>19</sub> | 2.5                              |      |      | μs   |

| CLK Rise time                      | t <sub>R</sub>  |                                  |      | 1    | μs   |

| CLK Fall time                      | t <sub>F</sub>  |                                  |      | 1    | μs   |

| Erase time                         | t <sub>ER</sub> | 2.5@ f <sub>CLK</sub><br>= 50kHz |      |      | ms   |

| Write time                         | t <sub>wR</sub> | 2.5@ f <sub>CLK</sub><br>= 50kHz |      |      | ms   |

| Power on reset time                |                 |                                  |      | 100  | μs   |

# **Timing Diagrams**

#### Figure 4 FM4442 Reset and Answer-to-Reset

### Figure 5 FM4442 Command Mode

上海复旦微电子股份有限公司 SHANGHAI FUDAN MICROELECTRONICS CO., LTD. FM4442 256 Bytes Memory Card Chip

Datasheet 9

Figure 6 FM4442 Outgoing Data Mode

Figure 7 FM4442 Processing Mode

Figure 8 FM4442 Break

上海复旦微电子股份有限公司 SHANGHAI FUDAN MICROELECTRONICS CO. LTD. FM4442 256 Bytes Memory Card Chip

Ü

# **Ordering Information**

| Ordering Code | Package                     | Product Carrier | Operation Range |

|---------------|-----------------------------|-----------------|-----------------|

| FM4442-P5-R   | Micro-Module Package (6Pin) | Reel            | -20°C ~ +60°C   |

| FM4442-M3-R   | Micro-Module Package (6Pin) | Reel            | -20 C * 100 C   |

Ü

# **Revision History**

| Version | Publication date | Pages | Paragraph or<br>Illustration | Revise Description                                                             |

|---------|------------------|-------|------------------------------|--------------------------------------------------------------------------------|

| 1.0     | Oct. 2007        | 10    |                              | Initial Release.                                                               |

| 1.1     | May. 2008        | 11    | Sales and<br>service         | Updated the address of HK office.                                              |

| 2.0     | Aug. 2008        | 13    |                              | Updated "Description"、"Electrical Characteristics" and "Ordering information". |

| 3.0     | Dec. 2008        | 13    | Sales and service            | Updated the address of Beijing office.                                         |

# **Sales and Service**

### Shanghai Fudan Microelectronics Co., Ltd.

Address: Bldg No. 4, 127 Guotai Rd, Shanghai City China. Postcode: 200433 Tel: (86-021) 6565 5050 Fax: (86-021) 6565 9115

### Shanghai Fudan Microelectronics (HK) Co., Ltd.

Address: Unit 506, 5/F., East Ocean Centre, 98 Granville Road, Tsimshatsui East, Kowloon, Hong Kong Tel: (852) 2116 3288 2116 3338 Fax: (852) 2116 0882

#### **Beijing Office**

Address: Room 419E, Bldg B, Gehua Building, 1 QingLong Hutong, Dongzhimen Alley north Street, Dongcheng District, Beijing City, China. Postcode: 100007 Tel: (86-10) 8418 6608 8418 7486 Fax: (86-10) 8418 6211

#### **Shenzhen Office**

Address: Room.1301, Century Bldg, Shengtingyuan Hotel, Huaqiang Rd (North), Shenzhen City, China. Postcode: 518028 Tel: (86-0755) 8335 3211 8335 6511 Fax: (86-0755) 8335 9011

Web Site: http://www.fmsh.com/